#198 January 2007

# CERCEUTER CONTRACTOR OF CONTACTOR OF CONTRACTOR OF CONTRAC

# THE MAGAZINE FOR COMPUTER APPLICATIONS EMBEDDED APPLICATIONS

# Self-Powered Data Logger

Build an Arbitrary Waveform Generator

New Uses for Flash Memory

Voltage Solutions

# The NetBurner Eclipse Ethernet Development Kit

Only

\$99

# **Featuring NetBurner's Eclipse IDE!**

One Click Compile and Load | Intelligent Code Completion | Integrated Debugger

# **The Complete Hardware and Software Solution**

Includes NetBurner MOD5270 Ethernet Core Module Performance and Memory | 32-Bit CPU | Freescale ColdFire MCF5270 147Mhz | 512K Flash Memory | 2MB SDRAM Device Connectivity | 10/100 Ethernet | 3 UARTs | I<sup>2</sup>C | SPI | 47 Digital I/O | SD/MMC Flash Card Support

> **Communication Software** TCP/IP Stack | HTTP Web Server | FTP | E-Mail | PPP | Flash File System

> **Development Software** NB Eclipse IDE | Graphical Debugger | Deployment Tools | Examples

> > **System Software** µC/OS RTOS | ANSI C/C++ Compiler and Linker

Product No. | NNDK-MOD5270LC-KIT Information and Sales | sales@netburner.com Telephone | 1-800-695-6828

# et Burner.com

# No code? No way.

Focus on your design and leave the coding to our PSoC Express™ visual embedded design tool.

- Support for our family of Programmable System-on-Chip™ (PSoC<sup>®</sup>) mixed-signal arrays—powerful, programmable digital and analog blocks with integrated MCU and flash memory

- Rich visual environment with simulation enables you to see your design and evaluate its performance instantly

- Built-in support for interdevice communication; seamlessly divide design problems into smaller pieces using multiple PSoC devices

- Retarget to any PSoC mixed-signal array at any time; design first and select device later

#### TRY IT OUT NOW.

Whether you have a minute or an hour to invest, we have a way to get you working with PSoC Express:

- View our online PSoC Express demo: www.cypress.com/expressdemo

- Request a FREE PSoC Express evaluation kit: www.cypress.com/expresskit

- Test drive PSoC Express at a live seminar near you: www.cypress.com/expresstour

- Download FREE PSoC Express software: www.cypress.com/psocexpress

Make all your embedded designs fast and easy. www.cypress.com/getexpress

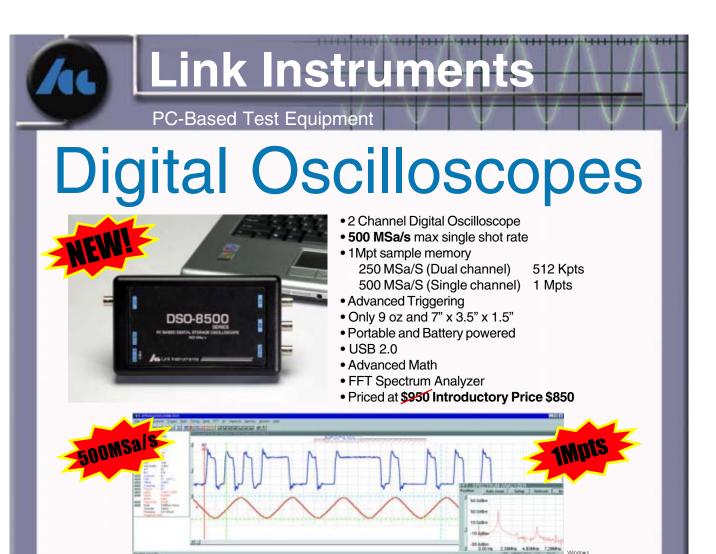

# Logic Analyzers

LA5240 (200MHz, 40CH) \$1700 LA5280 (200MHz, 80CH) \$2350 LA5540 (500MHz, 40CH) \$2500 LA5580 (500MHz, 80CH) \$3500 LA55160 (500MHz, 160CH) \$7500

- 40 to 160 channels

- up to 500 MSa/s

- Variable Threshold

- 8 External Clocks

- 16 Level Triggering

- up to 512K samples/ch

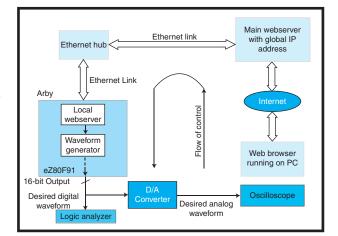

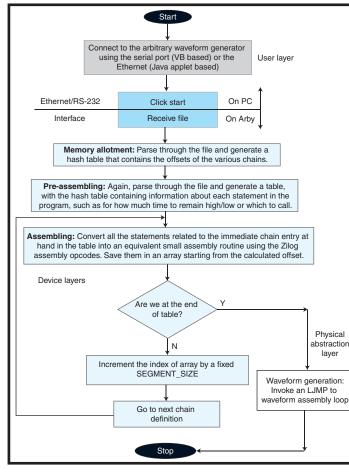

- USB 2.0 and Parallel Interface

- Pattern Generator option

Link Instruments (973) 808-8990 17A Daniel Road East · Fairfield, NJ 07004 · Fax (973) 808-8786 **WWW.Linkins4.com**

# RabbitFLEX A New Way To Customize

- Click-to-ship in 5 days!

Pay only for what you need

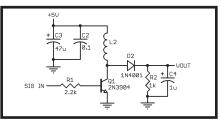

- Revision friendly

- Perfect for prototype and production

RabbitFLEX<sup>™</sup> is an unique build system that gives you the power to develop custom boards without the hassle and the cost. The RabbitFLEX simple-to-use web interface allows you to choose from numerous options such as digital I/O, analog I/O, serial ports, and Ethernet connections on your custom board. Just configure and buy online and our patent pending manufacturing process will deliver your solution in a matter of days. With RabbitFLEX you will reduce design risk, manufacturing cost, and development time. Start developing now by ordering the RabbitFLEX Tool Kit and your own custom RabbitFLEX board. Take your solution to the next level.

Configure and Buy Online www.rabbitFLEX.com

Quick-Turn Boards Range From \$149-\$279 RabbitFLEX Tool Kit <sup>5</sup>199

### **Test Drive RabbitFLEX**

Build your custom RabbitFLEX board online. Add a tool kit to your order for a complete development system including Dynamic C<sup>®</sup>.

www.rabbitFLEX.com

For a limited time with kit purchase.

2900 Spafford Street, Davis, CA 95616 Tel 530.757.8400 Solutions That Work

# TASK MANAGER

#### Agency vs. Contingency

When I was a student in London in 1998, I took an interesting sociology course titled Political Processes and Social Change. In his opening lecture, the course convener asked us a seemingly simple question: Is social change driven by contingencies or by the actions of human agents? Ah, yes, the old Agency vs. Contingency debate. Theorists who focus on the former tend to argue that individual actors such as Franklin D. Roosevelt, Winston Churchill, and Albert Einstein move history. In contrast, proponents of the latter theory argue that contingencies—such as pandemics and major fluctuations in the international markets—drive change.

What do you think, particularly in terms of the path on which the embedded community is traveling? Will the historians and social scientists of the future argue that it was the work of a handful of individual agents—particular designers, researchers, programmers, and corporations—that drove technological change, or will they write that various contingencies—such as macroeconomic changes in the technology sector—had the most impact?

Considering such questions will help you figure out where you fit in the puzzle. Do you believe a handful of engineers will develop the devices that will change the technological landscape, or do you think that exogenous social and economic forces will be main factors? Are you waiting for the next Bill Gates or market crash to determine your access to new technologies and your ability to design new systems?

Perhaps you should consider a completely different theory. The way we see it here at *Circuit Cellar*, the collective spirit and effort of the design community will lead the way. No matter which technologies, personalities, and socioeconomic variables (whether positive or negative) enter the formula for progress, the design community will remain steadfast in its determination to move forward and come up with novel ideas. If a young engineer develops a groundbreaking technology, the community will use it to its advantage. If the market should crash and hardware, software, and financial resources suddenly become scarce, the members of the community will work together to figure out ways around the problems. Sure, the speed at which the community will develop new technologies will change every year, but it's unlikely that any one person or event will derail the train. Are you on board?

It's exciting to see that many of you are now working harder than ever to develop your ideas and present them to your peers. Moreover, we're glad that you are actively addressing the social and environmental issues that are facing us in the 21<sup>st</sup> century. For instance, Abigail Krich, an enthusiastic designer who recently graduated from Cornell University's graduate program in electrical engineering, describes how she built a self-powered solar data logger (p. 12). She uses the system to measure solar insolation levels. This project proves that all of you can design effective systems that better the environment and society at large.

Columnist Jeff Bachiochi tackles another timely issue: alternative power sources (p. 56). He provides you with some tips on leveraging the power of "green" energy. Now is a great time to start thinking about the ways in which you can make your designs more environment-friendly and power efficient.

One last note: We're happy to announce the return of George Martin's Lessons From the Trenches column. This month, he begins a new series of articles about C language (p. 60). His articles will appear every other month.

cj@circuitcellar.com

C.abite

# **CIRCUIT CELLAR**

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

MANAGING EDITOR

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Jeff Bachiochi Ingo Cyliax Fred Eady George Martin

Ed Nisley NEW PRODUCTS EDITOR

John Gorsky PROJECT EDITORS

Steve Bedford Ken Davidson David Tweed CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> MEDIA CONSULTANT Dan Rodrigues

CUSTOMER SERVICE Debbie Lavoie

> CONTROLLER Jeff Yanco

ART DIRECTOR KC Prescott

GRAPHIC DESIGNER Mary Turek

> STAFF ENGINEER John Gorsky

ADVERTISING

860.875.2199 • Fax: 860.871.0411 • www.circuitcellar.com/advertise

#### PUBLISHER

Sean Donnelly Direct: 860.872.3064, Cell: 860.930.4326, E-mail: sean@circuitcellar.com

ADVERTISING REPRESENTATIVE Shannon Barraclough

Direct: 860.872.3064, E-mail: shannon@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster E-mail: val.luster@circuitcellar.com

> Cover photography by Chris Rakoczy—Rakoczy Photography www.rakoczyphoto.com PRINTED IN THE UNITED STATES

#### CONTACTS

- SUBSCRIPTIONS Information: www.circuitcellar.com/subscribe, E-mail: subscribe@circuitcellar.com Subscribe: 800.269.6301, www.circuitcellar.com/subscribe, Circuit Cellar Subscriptions, P.O. Box 5650,

- Hanover, NH 03755-5650

Address Changes/Problems: E-mail: subscribe@circuitcellar.com

#### GENERAL INFORMATION

860.875.2199, Fax: 860.871.0411, E-mail: info@circuitcellar.com

Editorial Office: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: editor@circuitcellar.com New Products: New Products, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: newproducts@circuitcellar.com AUTHORIZED REPRINTS INFORMATION

860.875.2199, E-mail: reprints@circuitcellar.com

AUTHORS

Authors' e-mail addresses (when available) are included at the end of each article.

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Vernon, CT 06066. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$23.95, CanadaMexico \$39.95, all other countries \$49.55. Nov-year (24 issues) subscription rate USA and possessions \$43.95, CanadaMexico \$59.95, all other countries \$45. All subscription orders payable in U.S. funds only via Visa, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-6650 or call 800.2696.301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the readers' jurisdiction. The reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright © 2006 by Circuit Cellar, Incorporated. All rights reserved. Circuit Cellar is a registered trademark of Circuit Cellar, Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

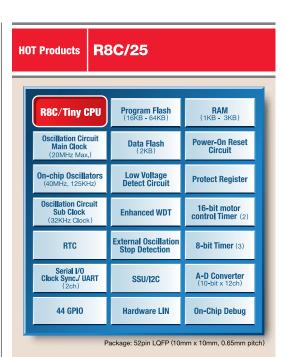

# **R8C/Tiny Brings 16-bit Performance to 8-bit Applications**

High-performance: 40MHz on-chip oscillator and single-cycle flash memory access

# **Renesas Technology**

#### No.1\* supplier of microcontrollers in the world

introduces the R8C/Tiny Series of microcontrollers. Its powerful 16-bit CPU core running at 20MHz provides the performance never imagined in 8-bit MCUs. R8C/Tiny MCUs high level of integration and peripheral set will enhance your application's functionality while reducing the overall system cost.

#### Top Reasons To Select R8C/Tiny High-Performance - 16-bit CPU runs at 20MHz, executing instructions in as fast as 50nsec. Scalable - Same core, same peripherals allows easy portability from 20 to 80pins High-Integration - Includes 40MHz on-chip oscillator, data flash, power-on reset circuits, several 8- and 16-bit timers, up to 20 channels of A/D, D/A, LIN, CAN and more Reliable - Oscillator stop detection circuits, access control of system registers - Watchdog timer with on-chip oscillator, programmable low-voltage detect circuit World-class Development Environment

- Complete software and hardware tools for short development cycle

- Free 64KB software tool chain

\*Source:Gartner Dataquest (April 2006) "2005 Worldwide Microcontroller Vendor Revenue" GJ06333

RenesasTechnologyCorp.

##

# **January 2007: Embedded Applications**

#### **FEATURES**

- 12 Self-Powered Solar Data Logger Abigail Krich

- 20 QuickComs An MC16C/62P-Based RS-232 Analyzer Nick Lott

- 26 Atmel AVR Design Contest 2006 Winners Announcement

- 30 Multi-Input Temperature Logger Nial Stewart

- 40 Arby An Arbitrary Waveform Generator with a Twist Dhananjay Gadre, Pushkar Sareen, Subodh Prabhu, & Suhas Chakravarty

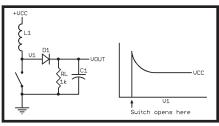

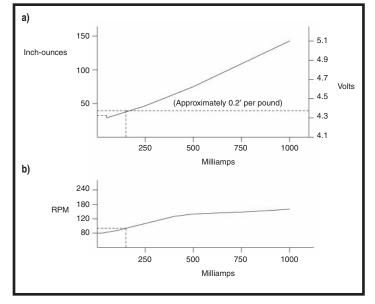

- 46 Voltage Solutions Harness the Power of Voltage Converters Stuart Ball

- 67 **The Power of Flash** Flash Memory Techniques for Your Toolbox *Mark Bereit*

#### **COLUMNS**

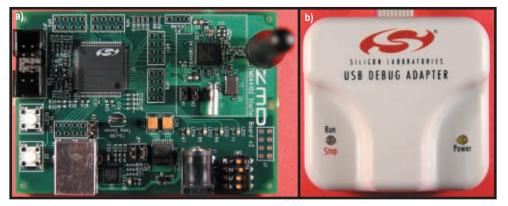

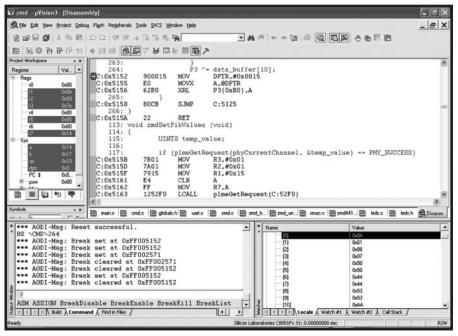

- 50 APPLIED PCs Dive Into the ZigBee Pool An Easy Way to Start Moving Messages Fred Eady

- 56 FROM THE BENCH Green Energy Jeff Bachiochi

- 60 LESSONS FROM THE TRENCHES Hello World ... Want Cookie George Martin

- 78 SILICON UPDATE Hot Chips 18 Tom Cantrell

#### DEPARTMENTS

- 4 TASK MANAGER Agency vs. Contingency *C.J. Abate*

- 8 **NEW PRODUCT NEWS** edited by *John Gorsky*

- 93 CROSSWORD

- 94 INDEX OF ADVERTISERS February Preview

- 96 **PRIORITY INTERRUPT** For Want of a Paper Trail *Steve Ciarcia*

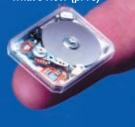

To meet the tough requirements to modern microcontrollers Atmel® has now combined ten years of low power research and development into picoPower™ technology for AVR® microcontrollers. picoPower enables AVR to achieve the industry's lowest power consumption with 650 nA with a real time counter running and 100 nA in deep sleep.

do for your design?

- What can AVR picoPower True 1.8V supply voltage enabling operation of all features and core down to 1.8V

- Minimized leakage current enabling 100 nA Power Down sleep consumption

- Sleeping brown-out detector enabling full protection with no power penalty

- Ultra low power 32 kHz crystal oscillator enabling operation at only 650 nA

# NEW PRODUCT NEWS Edited by John Gorsky

#### SYSTEM ON MODULE INTERNET APPLIANCE

The **SoM-NE64M** is a 16-bit system on module (SoM) based on the ColdFire MC9S12NE64 processor. This 16bit 68HC12-compatible processor has an Ethernet MAC and PHY built-in along with two serial ports. It features 64 KB of flash memory, 32 KB of EEPROM, and 8 KB of RAM. Another 512 KB of RAM can be added as an option.

All of this functionality is incorporated on a board smaller than a business card that uses less than 1 W of power. Applications for the SoM-NE64 can be programmed using GNU tools within an Eclipse IDE. Alternatively, the SoM-NE64 can be programmed using Code-Warrior.

Like other modules in the product line, the SoM-NE64M is designed to plug into a carrier board containing all the connectors and any additional I/O components that may be required. This approach allows the design of a custom carrier board that meets the customer's I/O, dimensional, and connector requirements without having to worry about the processor, memory, and standard I/O functionality. Since the module itself has more functionality built in than many other SoM designs, the carrier board can be much easier to design and produce, lowering cost and time to market.

In addition to the option of the developing a carrier board, one can be purchased off-the-shelf. Off-the-shelf carrier boards that feature A/D, D/A, MMC/SD card, keypad, LCD, and modem interfaces are currently available. The SoM approach provides the flexibility of a fully customized product at a greatly reduced cost.

The SoM-NE64M is ideal for any web/network data acquisition and control application. The SoM-NE64M costs \$67.

EMAC. Inc. www.emacinc.com

# **NEW PRODUCT NEWS**

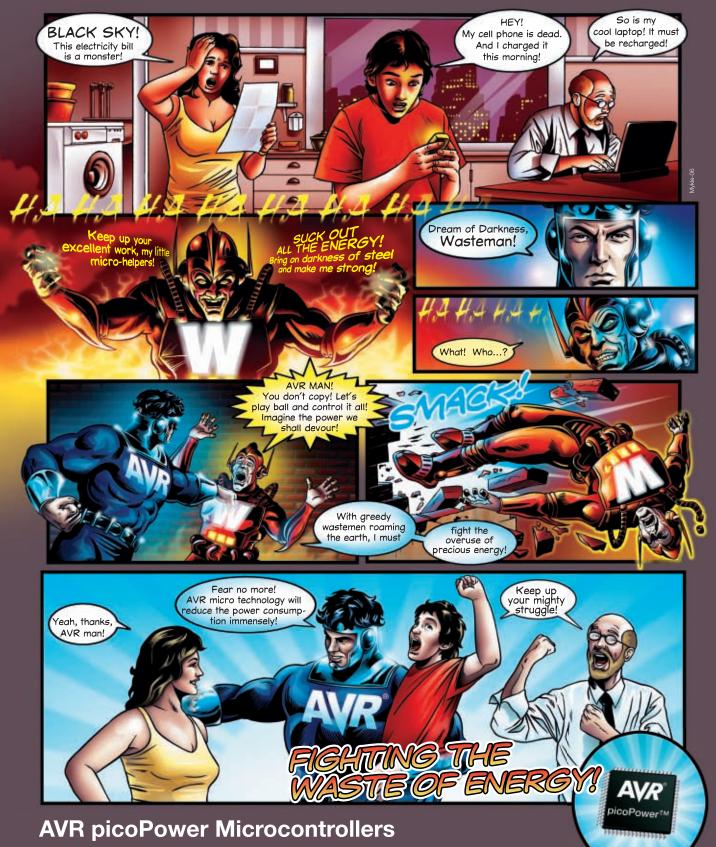

#### NEW IM3000.X ARCHITECTURE-BASED MICROPROCESSORS

The **IM3100**, **IM3300**, and **IM3900** are new processors based on the IM3000.x architecture. Each version has application-specific soft peripherals optimized for wired and wireless network applications.

This technology has three distinct advantages. Its reconfigurable architecture allows new peripheral functions to be synthesized and downloaded as microcode. Its field-programmable microcoded architecture allows the creation of custom instruction sets well suited for mobile and data communications applications. This results in very efficient, low-power operation. One version has been configured to execute Java byte code and does so with unprecedented efficiency. TCP/IP acceleration and encryption acceleration are included in the existing configuration libraries.

The IM3100 addresses the 802.11 wireless VoIP handset and terminal market with an integrated, narrowband, base band controller, Skype voice CODEC, LCD controller, and media and touch screen user interfaces.

The IM3300 enables the design of an optimized GPS positioning unit for fleet management applications. The GPS base band processor is implemented along with a number or serial and parallel I/O ports for communication to local sensors and the communications unit. The unit also incorporates an Ethernet controller.

The IM3900 is a general-purpose version that brings connectivity and Java together for embedded applications. This configuration constitutes a very efficient platform for program execution in assembly code, C, and especially Java. Ethernet and a multitude of other serial channels are available to provide a platform for communications protocol conver-

sions. The IM3900 implements a full Sun Microsystems certified Java ME–CLDC configuration.

Prices range from **\$12** to **\$15** in 10,000-piece quantities. The pricing includes licenses for software included in the basic chip configurations.

## Imsys Technologies AB www.imsystech.com

# **NEW PRODUCT NEWS**

Visit www.circuitcellar.com/npn for more New Product News.

#### SYSTEM ON MODULE WITH ULTRA-FAST LINUX BOOTUP

The **TS-7400** is a small embedded computer module (system on module) that is designed to provide extreme performance for applications which demand high reliability, fast bootup/startup, and connectivity at a low cost and low power, such as point-of-sales (PoS), vending machines, data acquisition units, and data recorder modules.

The module is based on the Cirrus EP9302 ARM9 CPU, which provides a standard set of on-board peripherals. The EP9302 features an advanced ARM920T 200-MHz processor design with MMU. The TS-7400 includes a standard SD Card socket and a 40pin header that brings out many interfaces, including audio, GPIO, and ADC. In addition, an one-piece setup with 802.11g Wi-Fi integrated inside a rugged enclosure is available, making this solution ideal for use in wireless sensor network, data acquisition/recorder applications, PoS, vehicle telemetry transmitter units, and more.

The TS-7400 has a tweaked boot-up firmware and Kernel that, along with the hardware accelerated NAND controller and hardware ECC, enables ultra-fast bootup to a Linux shell prompt in 1.1 s. The TS-4700 costs **\$99** each in 100piece quantities. Technologic Systems, Inc. www.embeddedarm.com

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

## FlashPro430 GangPro430

USB Flash Programmers for Texas Instruments' MSP430 microcontrollers.

MSP430 microcontrollers. Reliable and the fastest programmer on the market.

- Perfect for production usage.

60 kB Flash can be programmed in about 2 seconds

- supports JTAG, Spy-Bi-Wire and BSL interfaces

- can assign unique serial numbers

- v up to eight programmers can be connected to one

- PC and program target devices simultaneously

# Wow! Jameco just added 65,000 new major-brand products!

19,000 NEW

TEXAS

NSTRUMENTS

**3.000 NE**

5.000 NEW

PARTS

6.200 NEW

FAIRCHILD

PARTS

2,900 NEW

VISHAY

7,200 NEW FREESCALE PARTS

2,500 NEW

NATIONAL SEMI

PARTS

# The industry's fastest growing product offering!

You know that Jameco's catalog always offers over *99% in-stock availability*—the best of any electronic components distributor...

And now, they have the fastest growing product offering in the industry!

They've just added another *65,000 new parts* to their online catalog; and it's everything from ICs to passives, optos to interconnects, power supplies to electromechanical.

#### Service & Availability!

As Design Engineers know, Jameco offers great service, selection and same-day shipping!

Now you can get those same benefits for even more great brands...

-----

2,800 NEW

MICROCHIP

PARTS

2,500 NEW

MAXIM

PARTS

Check out these new and expanded lines:

**Aavid Thermallov** • Alcoswitch • AMP • **Amphenol Connex** • Atmel • Augat • AVX • Bourns • Buchanan • **Comair Rotron • Condor Power** Supplies • CTS • Cypress • Dallas Semiconductor • Fairchild • Freescale Semiconductor • Grayhill • Intel • Intersil • ITT • C&K Switches • Lattice Semiconductor • Lite-**On • Maxim • Microchip •** Micron Technology • Molex • National Semiconductor • Panasonic • Philips • Power-One • Raychem • **Renesas Technology** • Sandisk • ST Micro • Texas Instruments • Toshiba • **Tyco Electronics • Vishay** Intertechnology...

Get it here. Right now:

Jameco.com/CCU

Great Products. Awesome Prices.

# Self-Powered Solar Data Logger

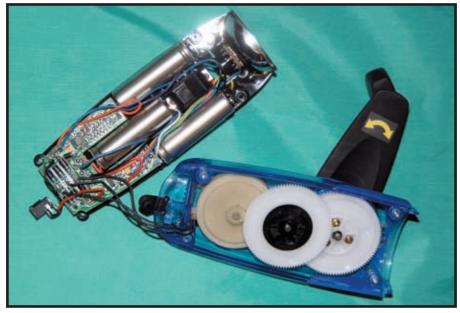

Abigail designed a microcontroller-based, self-powered solar data logger that uses a photodiode to measure solar insolation levels. The system converts the analog signal to a digital value that's stored in flash memory.

**U**n a seemingly rare sunny day in Ithaca, New York, the sun delivers about 1,000 W of power per square meter and just begs to be put to some purpose besides browning the backs of the students lying out in the gorges. At up to 15% conversion efficiency, COTS photovoltaics (PVs) can turn that light into electricity. A growing number of Ithacans have heeded the sun's call and installed solar electric PV systems to power their homes and businesses. Ithaca may get 40% less solar insolation than San Diego, but it gets 25% more than Germany, the world leader in installed PV capacity. Tompkins County, where Ithaca is located, has roughly 2.9 W of installed solar capacity per person, which makes it second in the U.S. to only Palo Alto, California.

With the Finger Lakes, ridgelines, and valleys cutting through the region, clouds and fog levels vary significantly from one part of town to another. But weather data is only available from a few select locations. How is a potential PV buyer to know how much power her system will produce unless they can measure the incoming light? And how can a proud PV owner know how her system is performing or detect faults unless she can confirm the conversion efficiency? Expensive commercial data logging systems that cost thousands of dollars do this well, but they are entirely unreasonable for the small system owner.

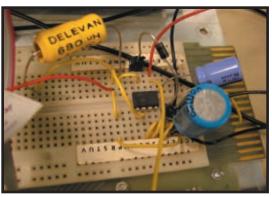

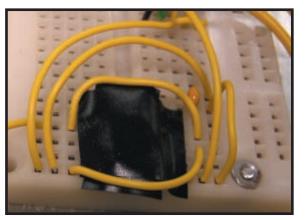

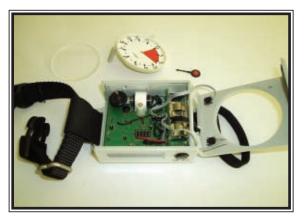

For Bruce Land's ECE476 Microcontroller Design course at Cornell University (http://instructl.cit.cornell.edu /courses/ee476/), I designed an inexpensive self-powered solar data logger to meet this need (see Photo 1). I built the system around an Atmel AVR STK500 development board that featured an ATmega32 microcontroller. You can leave the logger (untouched and isolated) in the field to collect data for months or years.

#### SYSTEM OVERVIEW

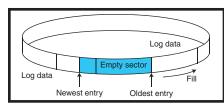

The solar-powered data logger features a photodiode that measures solar insolation levels and converts this analog signal to a digital value that's stored in flash memory. Every time the system logs a data point it also logs a time and date stamp so that the data can be downloaded to a PC and analyzed in the future.

When the system is logging, realtime data is displayed on its small LCD screen. The system displays several useful bits of information: the battery's voltage, the time and date, the length of time the system has been logging, and the length of time it can continue to log before running out of memory.

The logger has a dedicated solar power system that enables autonomous operation. A simple charge controller regulates the charging of a sealed battery (gel cell lead acid) by a small solar panel.

#### **APPLICATIONS**

When planning an off-grid solar elec-

**Photo 1**—Check out the complete solar data logger system with the PV panel, battery, and a mess of wires.

tric power system (one that isn't connected to a larger power grid), the output must be matched closely with the load in order to provide sufficient power without considerable waste. Although the price of photovoltaics has dropped by almost fivefold in my lifetime, it is still quite expensive.<sup>[1]</sup> Good planning and system design ensure that you can provide sufficient power without having to buy more PV than necessary.

The power output from photovoltaics is directly related to the insolation level. Although seasonal and annual average insolation levels for most major U.S. cities are available on the Internet, cloud cover and other weather effects can be extremely localized depending on the topography. Thus, the data for large cities isn't always the same as the data for the smaller towns in its vicinity. In addition, this data is not available for every part of the world. While accurate predictions of power output are important for grid-tied solar electric systems (in which the grid is used as 'storage' for any excess electricity produced and drawn upon for any electricity shortfall), this mainly impacts the return on investment expectations rather than the system sizing.

PV power systems are the only devices currently available for generating electricity without any moving parts. This makes them brilliantly simple and easy to care for, which is a real benefit for homeowners who do not want to spend their weekends greasing bearings and performing regular system checks. But without any maintenance needs or means for visual inspection, it is easy for system faults to go undetected for quite some time.

Large commercial PV installations typically have sophisticated sensors and monitoring software that can detect system faults and activate an alarm when maintenance is needed. These features are usually too costly for residential sized PV systems. The central component of these monitoring systems is an insolation sensor whose output is compared with system power production. When the power production strays significantly from what would be expected given the insolation, an alarm is triggered and maintenance checks can be performed. Although you may not need a fully automated, integrated monitoring system, some means for determining your PV system's efficiency enables you to perform maintenance only when it's necessary and to have peace of mind at other times that everything is functioning properly.

#### HARDWARE

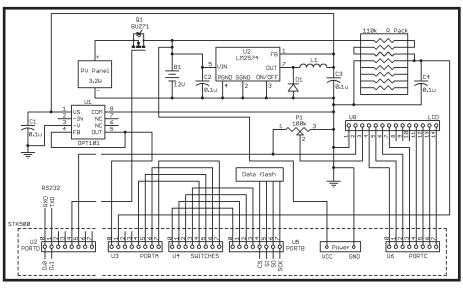

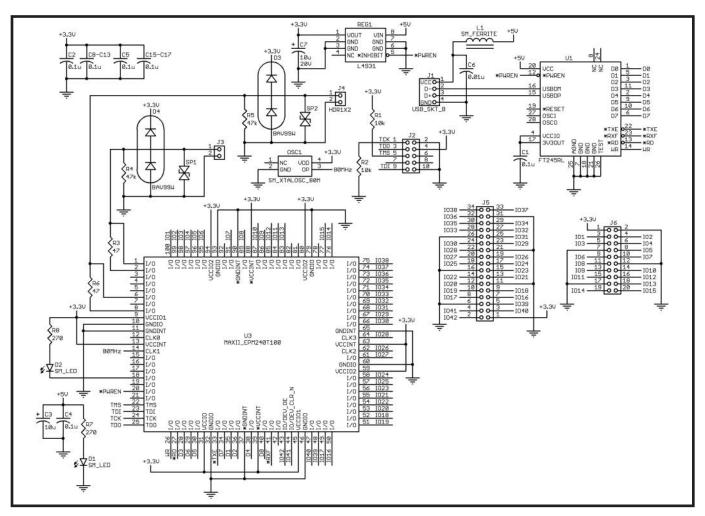

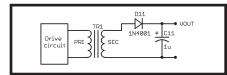

The system schematic is shown in Figure 1. The pins of the STK500 board are depicted along the bottom. Note that the RXD and TXD pins for the RS-232 connection and the data flash are also located on the board.

Port A connects to the photodiode and the switches. Port B also connects with the switches as well as the data flash. Port C controls the LCD and Port D sends data to the RS-232 connection and the field effect transistor. These ports connect to the ATmega32 microcontroller.

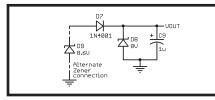

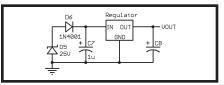

#### POWER SUPPLY

The logger has a dedicated solarcharging system to enable for autonomous operation. It was built around a 3.2-W solar panel a Volkswagen dealer gave me to accessorize the originally diesel-fueled Volkswagen Golf TDI that I bought and converted to run on vegetable oil. But that car is another story.

Even without much optimization for efficiency, the power needs of the logger are very small. The maximum power drawn by each of the main components is 5 mW for the LCD, 75 mW for the ATmega32, and 75 mW for the photo-

Photo 2—The LM2574 step-down switching regulator maintains the voltage supply to the logger at 5 V.

diode for a total of 155 mW. If all components run at maximum power at all times, this would amount to 3.72 Wh/day. This does not account for losses in the voltage regulator or other minor components, but there is plenty of energy available for the system so this is not a problem.

The battery I chose was a 12-V, 5-Ah sealed gel cell lead acid deep cycle battery. This type of battery is the most cost effective when size and weight are not a concern, but safety, ease of handling, and the ability to deep-cycle the battery are. Although a 12-V, 5-Ah battery could provide 60 Wh, draining any battery too low (even a deep cycle battery) can cause damage. Five days of energy storage in Ithaca is considered conservative, but due to the reliability needs of an autonomous system such as this, it is worth having a good factor of safety. Note that 37 Wh of useful storage enables the system to ride through 10 days with no sun, giving plenty of leeway with the battery chosen.

Even with enough storage, it is necessary to be sure that the energy balance of the system is kept positive or the battery will eventually drain. Ithaca averages 2.3 sun hours per day in the winter.<sup>[2]</sup> What this means is that a solar cell rated at 1 W would produce 1 Wh of electricity per sun hour. My 3.2-W solar panel would therefore be able to produce 7.4 Wh (on average) of electricity per day during the darkest time of year in Ithaca if kept at its maximum power point. Because there is no maximum power point tracking in this system, it can be expected that the panel will produce about 5.2 Wh per day in the winter, which still

far exceeds the maximum load expected.

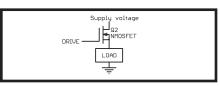

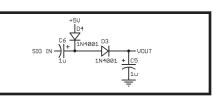

The PV panel, which is rated at 18.8 V at its maximum power point, was designed for trickle charging a 12-V car battery and so could be directly connected to the data logger. However, to prevent battery damage from overcharging, I needed a way to disconnect the panel once the battery was fully charged. Using a BUZ71 field effect transistor and a polling routine, the panel was effectively disconnected when the battery voltage rose above 12 V.

Depending upon the state of charge, the battery voltage will float around 12 V but will not remain steady. The logger components required a constant 5-V power supply. The ON Semiconductor LM2574, a 0.5-A, 5-V step down switching regulator (buck converter) regulates the voltage from the battery to the level needed for the system components (see Photo 2). This regulator has a typical efficiency of 72%, which is much higher than resistance-based voltage regulation.

An unresolved and bizarre result of running the logger off of the solar power supply as compared to the standard AC/DC power supply was that the on-off switch on the STK500 ceased to function. The only way to turn the logger on or off when connected to the solar power supply was to actually disconnect a battery lead.

#### PHOTOSENSOR

A Texas Instruments OPT101-a monolithic photodiode and single-supply transimpedance amplifier-is used to sense the incoming solar insolation level. Natural sunlight ranges in intensity from 0 to approximately 1,000 W per square meter, but the OPT101 puts out its maximum voltage at roughly 10 W per square meter of incident insolation. With hardly any light striking the sensor, it reached its upper limit. It was thus necessary to attenuate the intensity of the light striking the photodiode to increase the range over which the sensor could differentiate intensity.

Ideally, this would have been done with neutral density filters, but I didn't

**CIRCUIT CELLAR®**

have any on hand. I used the next best scientifically accurate and available tool: electrical tape. Two layers of electrical tape covering the photodiode were found to be quite effective. This solution enabled the sensor to give reasonably reliable readings over the full range of expected intensities (see Photo 3).

The microcontroller's ADC has a maximum value of 255. Multiplying by a factor of four roughly converted the ADC reading to watts per square meter. Ideally, this system would be calibrated and the factor would be more precise than four, but this approximation gave reasonable results with a range of readings from 0 to 1,020 W per square meter.

I used the ATmega32-based STK500 development board because of its integral flash memory and switches. However, if this system were commercialized or rebuilt, it is fairly obvious that the STK500 would not necessarily be used. It has many features that are unnecessary for this project. A far simpler and more com-

Figure 1—The system's schematic shows the STK500 and its connections with each of the other components.

pact board can be designed.

#### PROGRAM

An interrupt-driven program runs the system and enables accurate timing. An interrupt service routine decrements a series of task timers once per millisecond. The main task in the program calls various subroutines at predetermined intervals when their task timers run out and the appropriate flags are set to enable a task to run. Each of the eight buttons is polled separately once every 30 ms with a state machine to debounce the button as it stabilizes after a transi-

tion. The only button that is not debounced is the LCD Wake button because bouncing is not a concern with this function. The debouncing routine is based on code written by Bruce Land.

Each time the system is turned on or reset, it welcomes the user and guides her through the set-up process (see Photo 4). During set-up, you set the system time and date, select the logging frequency, decide whether to clear any stored data or to continue by appending future data, and indicate when to actually begin logging after the system is in place.

In order to enable data appending after a reset, the memory pointers have to be stored in nonvolatile memory and initialized only when the chip is programmed, not each time the system is reset. The ATmega32 contains 1,024 bytes of data EEPROM memory organized as a separate data space in which single bytes can be read and written. The pointers to the flash

**Photo 3**—The photosensor is covered with two layers of electrical tape to provide a larger range of sensitivity. The inset shows the sensor without the tape cover.

memory as well as a log of how long the system has been logging are kept in EEPROM. During operation, you can reset the time if needed or change the logging frequency without interrupting the data collection. If the logging frequency were changed, it would be impossible to calculate how long the system had been logging unless a running tally had been kept.

A series of flags and state machines

are used throughout the program to prevent erroneous user input from activating a section of code out of order. At any given point in the program, only the relevant buttons are active and their functions change as shown in the button labels in Photo 5.

The battery voltage and the photodiode output are fed into two channels of the ATmega32's ADC. The ADC has a maximum input of 5 V. So, in order to read the battery voltage, it was necessary to use a voltage divider to guarantee that the

input to the ADC was within range. Initially, the system sampled only the light level with the frequency at which the user wanted data stored. However, with logging frequencies of 1 min. to 1 h, this did not allow for a satisfying real-time display that showed changes in light intensity. Moreover, it allowed less accuracy if only one sample was taken per stored data point. Instead, the final design

Photo 4—The data logger greets users before leading them through the system setup.

reads the ADC once per second through a task that enables an ADC interrupt routine and starts a conversion. The ADC interrupt automatically switches between the two channels for the photodiode and the battery voltage, reading the battery voltage once for every five times the photodiode is read.

To get an accurate battery voltage reading, the PV panel is disconnected just before the reading is taken and then reconnected immediately after if the battery voltage is below 13 V. If it is at 13 or above, the PV panel is not reconnected to prevent overcharging.

The instantaneous readings are displayed to the LCD screen and kept in a running average over the logging interval. When the logging interval is complete, a data point is stored in the flash memory and the running average is cleared.

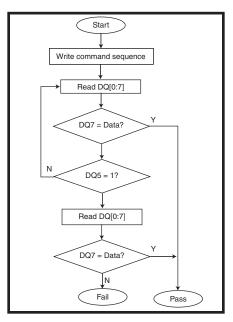

To be able to run for a useful length of time, the data logger needed an external memory for storing measured data. The older STK500 boards have flash memory chips built into them (as can be seen on the upper right of the board in Photo 5), making this an obvious choice. Unfortunately, I did not have any instruction set for interfacing with the flash memory. An earlier ECE476 project used this flash memory. Based on the project's code and comments, I was able to learn how the flash memory interface worked.<sup>[3]</sup> The designers used a program named dFlash, which was written by Terje Frostad of Atmel Norway. I e-mailed the Atmel AVR technical support team and received permission to use dFlash in my project as well. The dFlash program provides a set of routines to interface with the flash memory by writing to a 264-byte buffer. This buffer is then written to

one of 1,024 264-byte pages of the flash memory.

Because the routines take byte-size data as input, I had to break the insolation value (stored as an integer) into 2 bytes and then put it back together again when storing or retrieving it. The 2-byte insolation together with the time and date stamp meant that each time the system logged a data point it used 8 bytes of memory. This allowed the system to log 33,792 data points. The logging interval is user-selectable from 1 min. to 1 h. At an interval of 1 min., the system is able to continuously log data for 23.4 days before filling the memory. At an interval of 1 h, the system is able to log for 3.8 years.

One thing I did not realize that caused me a considerable headache was that PortB.4:7 is used for interfacing with the flash. I had initially been using PortB as input for the switches, but I found that three of the switches ceased functioning properly. When I realized that dFlash was reinitializing these pins, I was able to switch these buttons to PortA.

The flash memory can be read either through a buffer or directly, the latter being my choice for the logger. If you were to call for the data to be retrieved before the buffer had filled and written the data to flash, there would be no data to retrieve. Thus, it was necessary to write the buffer to flash memory just before the data retrieve routine was entered as well as when the buffer became full. It was also necessary to give the microcontroller a brief period to finish writing the buffer before the read command was executed or the same problem would occur.

The read command is executed when you press the Retrieve Data button (active only when the logger is stopped). The logger must be connected to a computer using an RS-232 cable with straight-through connection. You should start a simple terminal program on the PC (e.g., HyperTerminal) set to 9,600 bps, no parity, 1 stop bit, and no flow control.

When the Retrieve Data button is pressed, the system prints identifying header rows followed by a row for each data point logged with the time and date at which it was stored. The LCD displays the message "Uploading

# How far will your design take you?

Challenge yourself against other top embedded engineers around the world in **DesignStellaris2006**, proudly sponsored by Luminary Micro, Keil, and Circuit Cellar.

Use any microcontroller in Luminary Micro's Stellaris™ family of ARM® Cortex™- M3 controllers with the ARM RealView® Microcontroller Development Kit (MDK-ARM) to create your design contest entry, and see how far your design will take you!

- No purchase necessary to enter.

- \$10,000 in cash prizes!

- Entry deadline is February 7, 2007.

- Winners will be announced at the Embedded Systems show... Silicon Valley 2007.

- Submit your design today!

FOR COMPLETE DETAILS, VISIT www.LuminaryMicro.com/ DesignStellaris2006

**THE LM3S811 EVALUATION KIT includes** the Stellaris LM3S811 Evaluation Board, an evaluation copy of MDK-ARM, USB cable, documentation, and programming examples.

Data" followed by the time and insolation value presently being uploaded. Upon reaching the end of the data, a footer row is printed to the terminal program and the LCD displays the message "Done Uploading Please Restart." The data in the terminal program on the PC may then be copied into another program for storage or analysis. If an incomplete transmission was made, you may reset the logger and choose to upload the data at the first prompt. The data may be uploaded as many times as the user desires until the memory is cleared.

Initially, the program was written with each of the subroutines that updated a parameter sending its update to the LCD. This avoided updating the LCD more frequently than necessary. However, when power-saving code was incorporated to turn the LCD screen off when the system was idle by driving it with a port pin, the system would freeze every time it went idle. It turns out that the LCD sends and receives messages to and from the microcontroller. If the LCD is off when the microcontroller sends it a message,

**Photo 5**—Check out the STK500 board with labels for each of the eight buttons.

it is not able to respond and the microcontroller hangs, waiting. The program thus had to be rewritten to prevent the LCD from being called when the LCD screen was turned off. I did this by writing a single routine that printed to the LCD screen. A state machine and a variety of flags controlled it so that the correct message would be displayed.

Additionally, there was some difficulty at times with the LCD not making proper contact with the surplus whiteboard I was using. When the LCD lost contact momentarily, it would cause the system to freeze. Thus, I added an extra new whiteboard solely to hold the LCD screen securely because I was not able to solder the borrowed LCD to my project. Another problem I had with the LCD was when the STK ground was not properly connected to the system ground, the negative terminal of the battery. This happened during testing with the STK500 plugged into an AC/DC power supply. When the two grounds were not at equal voltages, the voltage across the LCD was not in its operating range. The positive voltage was coming from the STK port pin and the negative voltage from the battery negative terminal. Once the two systems were joined by connecting to the STK ground pin (or also powering the STK from the battery), the LCD resumed

normal operation.

#### **IMPROVEMENTS**

If I rebuild this system for fun or commercialization, it will need to be packaged in a weatherproof enclosure to allow for outdoor operation. Additionally, since not everyone has a spare PV panel lying around the house, it would be important to increase the system's efficiency to allow for a reduced panel size because this is the most expensive component. This can be done in many ways.

The first way would be to have a maximum power point tracking charge controller rather than the simple on-off switch used in this project. This would keep the voltage of the solar cells at the maximum power point on the I-V curve. It would effectively extract about 30% more power from the panel than allowing the battery to determine the panel's operating voltage. The second way to improve efficiency would be to reduce the power consumption of the system. Because I had plenty of power from my PV panel and sufficient battery capacity, there was no need for this system to do more than turn the LCD screen off when idle. However, it would be possible to reduce power needs further by reducing the chip's clock speed, letting the chip go idle between readings or at night, and eliminating the LEDs on the STK500 board or using another board entirely.

The sun was shining in my eyes as I started working on this article last summer. I think I'll soon have to join the fold and get a PV system of my own to go with the logger.

Abigail Krich (ajk28@cornell.edu) holds a B.S. in biological and environmental engineering and a Master's degree in electrical engineering from Cornell University. She is now a project developer at Tamarack Energy, a renewable energy development company. She has previously worked at the National Renewable Energy Laboratory's National Wind Technology Center and at Northern Power Systems.

#### **PROJECT FILES**

To download the code, go to ftp://ftp. circuitcellar.com/pub/Circuit\_Cellar /2007/198.

#### REFERENCES

- R. Wiser, M. Bolinger, P. Cappers, and R. Margolis, "Letting the Sun Shine on Solar Costs: An Empirical Investigation of Photovoltaic Cost Trends in California," LBNL-59282, NREL/TP-620-39300, 2006, http://eetd.lbl.gov/ea /ems/reports/59282.pdf.

- [2] Solar Insolation for Major U.S. Cities, Advanced Energy Group, www.solar4 power.com/solar-power-insolationwindow.html.

- [3] S. Jean-Louis and C. Pandarinath, "The Big Red Guide," ECE476 Final Design Project, Cornell University, 2004, http://instruct1.cit. cornell.edu/courses/ee476/Final Projects/s2004/sj74/main.htm.

#### RESOURCE

Datasheets, dFlash.c, and the User Guide, http://instruct1.cit.cornell.edu /courses/ee476/FinalProjects/s2006/ ajk28/ajk28/index.html.

# QuickComs

## An MC16C/62P-Based RS-232 Analyzer

Although RS-232 is disappearing from new devices, you'll probably have to work with it from time to time. You can connect Nick's M16C/62P-based system to an RS-232 device to determine the correct data rate, wiring, and encoding scheme. You can also use it to monitor a serial link.

The inspiration for this project came from various sources and situations, including my own debugging of old lab equipment, the need to quickly diagnose a broken serial link in a microcontroller system during the design phase, the need to quickly debug student designs in a teaching lab environment, and the need to assist those without an oscilloscope to determine the communication parameters of old equipment.

A few years ago, a friend of mine who was developing front-end systems for databases was given a project that needed to communicate with some electronic scales. He was given scales and cables, but that was it: no data rates, parity bits, or stop bit information. I was asked if there was an easy way to determine the device's communication settings. I asked if he had a scope. "A what?" was the reply. Eventually, he figured out by trial and error that the device used 1200-7e1. I thought there should be a better way.

For me, figuring out the exact data rate and encoding and wiring scheme for the serial connection on that really old piece of equipment at the back of the lab has always been part of the fun and challenge of being an electronics technician. But then again, not everyone can just run off and grab an oscilloscope or logic analyzer and come up with an answer. Sometimes having to repeat the process 10 times in a single lab session as students learn the ins and outs of working with microcontrollers can be a bit tedious and take some of the fun out it. These are some of the reasons why I designed the QuickComs prototype.

With RS-232 quickly being replaced by USB, I hope the nightmare of incorrectly wired appliances and forgotten data rates will be a thing of the past. Unfortunately, RS-232 will still be with us for a long time to come, and as it becomes used less frequently, the exact parity and data rates for devices will be easily forgotten.

#### QuickComs PROJECT

QuickComs is a useful M16C/62P microcontroller-based system that can be connected to an RS-232 device to determine the correct wiring, data rate, and encoding scheme. It can be used to monitor a serial link as well as act as an automatic null modem cable. Quick-Coms can be inserted inline to a serial link or connected to a single device.

This project should be useful to anyone who often works with older scientific or industrial equipment. You'll also find it useful if you need to quick-

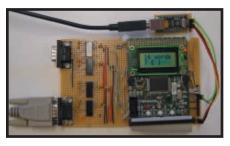

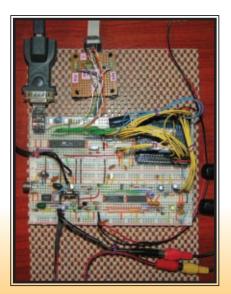

**Photo 1**—*I* built the prototype using the SKP16C62P demonstration board, some strip board, and a handful of ICs that I had lying around. The process was fairly quick and easy.

ly troubleshoot a serial connection in a microcontroller system. It has already proved useful for quickly revealing situations in which the system or UART clock was running at an unexpected speed. This is fantastic in a teaching lab when a student's breadboard circuit doesn't work the first time. If you don't have an oscilloscope, this system gives you the power to determine the communication parameters of equipment. You don't need to have an in-depth understanding of the technology. It's a turnkey solution for the front-end developer.

As you can see in Photo 1, the current design is only a prototype. As such, it isn't as portable as a commercial product (nor is it as pleasing to look at). But I imagine it would be quite straightforward to take this design and optimize it for commercial production in a package not much larger than a standard deck of cards (similar to the Atlas range of products from Peak Electronics Design).

#### SYSTEM OPERATION

The device has a number of different displays and modes. Each summarizes different information about the serial link. The system operates completely via two of the three buttons: S1, S2, and S3. These are located from left to right across the bottom of the Renesas Technology SKP16C62P demonstration board.

The S2 and S3 buttons are used to navigate the display system. S3 acts as a Next button that moves the system through the modes of analysis. S2 acts as an Enter button for selecting options from the menu.

In the initial display, the device shows the status of the two serial connections DE9F and DE9M, the female and male connectors, respectively. If a cross-wired cable is detected on a port, then "Xvr" will be displayed next to the name of the port. If the port is disconnected or isn't detected, then it will not be shown on the display. If neither port is in use, then a "No Cable Detected" message will be displayed. When at least one port is detected, you can move on to other displays. If both serial ports are being used, then data rate detection and analysis will occur only on the DE9F connector. To detect on the DE9M port, simply remove the DE9F cable.

The voltage display shows the RS-232 voltage levels. These voltages are measured on the RECEIVE pin of each input. S2 changes the display format to include two decimal places. It's this voltage that is used to detect the presence and polarity of a cable. This information is a useful check for ensuring that the serial link's hardware layer is present and operational.

Monitor mode is used to initiate communication on the USB connection to allow third-party monitoring of the data sent and received on the DE9 connectors. The USB connection uses the same data rate and settings as those detected on the DE9 connectors. S2 is used to toggle the USB connection on or off.

The number of events detected on the RS-232 lines is available as a Display mode. The device has a maximum number of 128 events that can be analyzed. The event memory resets automatically if there is a 1-s pause in data on the

serial line. Pushing S2 can also clear the event memory. When an event is detected, the green LED illuminates.

The period display is used to show the width of the shortest pulse in the event memory. This is used to calculate the data rate. Again, S2 changes the display format to include decimal places. The display will automatically change units between microseconds and milliseconds where appropriate.

In addition, the exact data rate calculated from the bit width is available. As with other displays, S2 changes the display format to include a decimal place. The data rate is displayed in bits per second. This information is useful when a microcontroller has been set up incorrectly or when a clock has gone haywire and is no longer using a standard data rate.

Although the given bits per second

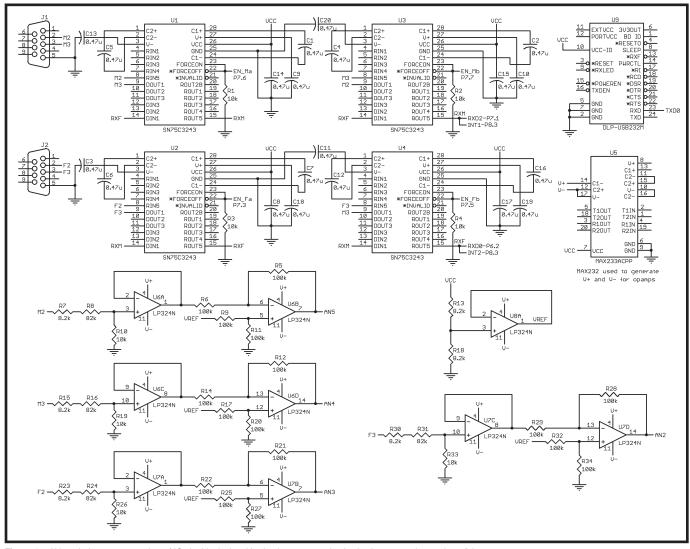

Figure 1—Although there are a number of ICs in this design, it's simply some very basic circuits repeated a number of times.

value is useful, it is often slightly wrong due to timing inaccuracies and it doesn't always give a usable value. The data rate Guess mode calculates the closest commonly used data rate from an internal table of standard data rates. The top line of the display shows how close the measured data is to the guess. A value less than 90% usually means the guess is wrong. This information can be a very valuable ballpark figure when you are beginning to debug a serial link.

If the data rate guess looks good

enough, you can then go on with some analysis of the data in the event memory using the guessed data rate. If no reasonable data can be found, then "NoMATCH" is displayed. If the parity bits can't be determined, the display will read "xx bit," where xx is the number of bits per word including start, stop, and parity bits. The top line displays the number of complete words or characters used in the analysis. If you have a good data rate guess (better than 98%) and a decent num-

ber of events (more than 32 or so), this is usually bang on the money.

#### HARDWARE

Renesas Technology's M16CM30626 was a great choice for this design because of its three flexible UARTs and its large memory. I used the SKP16C62P development kit to help reduce development time. I found it useful because it contained all of the basic input and output hardware, and it brought all of the ports out to userfriendly 0.1" headers.

The full-featured development environment provided by the High-Performance Embedded Workshop in combination with Renesas's interactive on-line labs gave me a great head start for learning about this microcontroller family. Using these tools, I could get to grips with the environment and hardware virtually while the real hardware was in the hands of FedEx. This enabled a great start to the project, and when the actual hardware arrived, I was ready to start my specific application development.

As you can see in Figure 1, the circuit is based on a number of RS-232 line drivers and receivers (Texas Instruments 75C3243). Two of these are used on each input and have crossed wiring. When the system starts up, all of the transceivers are disabled. The firmware then looks at the voltages on the signal pins of the connectors and enables the appropriate transceivers.

#### **TRANSCEIVERS & LINE DRIVERS**

Two transceivers were used for each RS-232 connection. I used Texas Instruments 75C3243 ICs because they were available at the time. For a future design, I'm considering using a dual or even quad transceiver chip such as the 64C232343 to lower component count.

This system was not designed to be the most inexpensive solution, but I wanted it to be easy to construct. The drivers were chosen simply because I had them on my workbench. If you want to build a similar system, any driver with a high impedance or Shutdown mode would be suitable. In operation, an individual select line enables each chip. At most, only one chip is ever active per channel at one time to avoid driver contention issues.

The chips operate in three modes. In High Impedance mode, both chips are disabled. This state is used to examine the voltages present on the communications line with no excitation from the on-board drivers. With the first chip selected, the channel is in Normal mode. In this mode, the pins of the DE9 are connected in standard configuration with pin two corresponding to the RXD (input) signal and pin three as TXD (output). In this configuration, the second chip is disabled. Lastly, in Crossover mode, the second chip is selected and the first is disabled. The second transceiver is wired with opposite connections to the DE9. This will have correct connections for a crossover/null modem cable. To keep the circuitry simple, only TXD and RXD signals were used. Flow control signals such as CTS, RTS, and DTD could have been added, but they weren't used due to time constraints. This set up is repeated for each channel.

The TTL logic sides of the two transceivers are connected in parallel and then cross-wired and connected between channels. This ensures that the two channels have a correct connection. TXD from channel 1 (DE9M) is connected to RXD on channel 2 (DE9F). As a result, there are only two TTL signals on the schematic: RXF and RXM. These signals are connected to RXD1 (P6\_2) and RXD2 (P7\_1) on the demonstration board. This enables you to monitor the communications on each port individually. This crossover of the transceivers on the TTL logic side enables the system to function as an automatic null modem cable with minimal overhead on the microcontroller system. All the microcontroller has to do is simply enable the appropriate transceiver for each channel.

To enable the measuring and analysis of raw serial data, these signals are also connected to two of the external interrupt channels: INT1 and INT2. This enables the system to accurately detect level transitions.

#### **VOLTAGE SCALING & SAMPLING**

In the initial state, all transceivers are off, and the built-in ADC measures the external voltage on the pins. A separate channel of ADC and op-amps (giving four channels in total) sample each pin voltage.

The voltage on each SIGNAL pin is monitored with some basic op-amp circuitry. This is done to scale them from possible inputs of  $\pm 25$  V to the 0 to 5 V available to the microcontroller. The pin voltages are first scaled using resistors and then buffered using a voltage follower. The voltage is then inverted and shifted. This centers it on the reference voltage. The reference voltage is half the microcontroller supply voltage ( $V_{CC}$ ) and is created by a simple resistive divider and a buffer. I initially considered multiplexing these signals through a single input stage, but I decided to go for the brute force approach for two reasons. First, opamps are generally cheaper than analog multiplexers. Secondly, with the SKP16C62P, I had inputs to burn. In fact, four ADC channels are hardly a big request for any modern microcon-

troller these days.

A fifth RS-232 driver was used simply to generate the  $\pm 10$  V for the op-amp voltage rails. This was a MAX233ACPP. I just so happened to have one still sitting on my workbench. It did the job nicely. I didn't need any external parts. For my future design, this will be eliminated. I will use either the existing drivers or a less expensive, more efficient, solution. Using this independent voltage generation enabled me to have all of the 75C3243 ICs in Shutdown mode until I had ascertained the correct connection polarity.

#### CONSTRUCTION

I used strip board to mount the components and the SKP16C62P. It was a good choice because the simple external circuitry consists of mostly through-hole components. The transceiver chips were all SMD 1.27-mm pitch small outline packages (SOIC). To mount the chips, I simply ran uninsulated wire through holes in the strip board and then soldered to the pins on the chip sitting on the component side of the board. I was able to use this technique because a large number of the pins remained unused in the design. This has proven to be a pretty robust technique. All of the chips are held firmly in place and have managed to withstand a fairly rough life on my workbench.

I mounted the demonstration board using standard PCB stand-offs over the sampling and scaling section. Photo 2 shows the component side of the board with the Renesas board folded out of view.

I connected the circuitry to the demonstration board using an old 50way IDC ribbon cable that I had in a box of junk. This was great because it enabled me to quickly and easily disconnect the demonstration board when I wanted to use it in other M16C projects and experiments. Any unused wires were simply tied back in a neat bundle and moved out of the way. If you have a keen eye, you'll notice that the hook-up wire is mostly single core from a salvaged length of twisted-pair telephone network. There

Photo 2—When you remove the Renesas Technology hardware from the prototype, you're left with a relatively basic set of electronics.

are a few 0.1- $\mu$ F decoupling capacitors not shown on the bottom of the board.

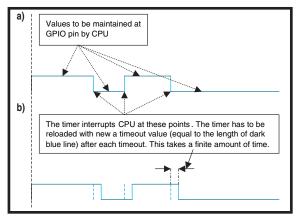

#### SOFTWARE

Data rate analysis is achieved by using a 16-bit timer and information obtained from the external interrupts (INT1 and INT2). The time lapsed between each event is recorded in a buffer using the 16-bit timer. The timer is free running with any overflows recorded between external interrupt events.

The software sets the internal timers to 3 MHz (the main clock divided by eight). This gives a frequency resolution of 333.3 ns. In order to be used for other human interaction events, the timer is set to reset every 5 ms. At this point, an overflow is recorded, LEDs are updated, and a data timeout is checked for.

Although mostly redundant, the logic level after the event is also recorded. The levels are recorded as single bits, whereas the main event time array stores the timer values as 32-bit numbers. The event memory is reset if no events have occurred for 1 s. In its current form, the software has memory for up to 128 events. At a standard 8N1 encoding, this equates to at least 12 characters. This may seem like a very small data set, but in practical tests, it was found to be plenty. The event times are stored as raw clock counts.

When designing the software for the analysis, I aimed to simply mimic the actions I would manually take and automate them. The trouble with this approach was that so much of successfully tackling these problems in real life relies on educated guesswork from prior experience. I was able to emulate this through the use of a simple data rate table because a standard data rate is used more often than not. (Students are often amazed when looking at a rough 100-µs pulse. They tend to say, "Hmm, I bet that's 9,600 bps.")

I thought of using a similar trick for the encoding schemes, but I felt it was better to go for a brute force approach. This makes it possible to find that one-off crazy setting that you would

never use yourself. My manual approach is to try different encoding schemes in the order of popularity (based on my experience). I usually start with 8N1, 7N1, 8E1, and so on until I see some data that looks about right. With the speed of the microcontroller, it is fast enough to simply try every valid possibility. Of course, the other difficulty is defining exactly how to quantify "about right" in terms of C code and arrays of data. Luckily, that is something UARTs do every day. It is well documented. I found Jan Axelson's book, Serial Port Complete, to be extremely helpful in this respect.

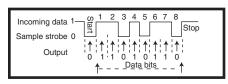

#### DATA RATE

The shortest event is easily used to determine the data rate. Selecting the closest value from a table of common data rates then normalizes it.

The event data is then converted from time data to bit length data using the nearest data rate. So, a 300-µs event is said to be 3 bits long if the selected data rate is 9,600 bps. This data is then used to look for consistent positioning of start, stop, and parity bits.

#### **ENCODING**

When I first wrote the software for this project, I called it a "statistical analysis." I don't know if this term is really correct, but the idea is to simply try everything and see how often it's right. I then just simply pick the best solution. This type of software is, of course, only as accurate as the sample data. It's prone to being wrong for rather small sample groups. The more astounding thing was its accuracy.

The first part of the encoding analy-

sis is a simple routine that looks for start and stop bits and then counts the number of times it has successfully found a word at a given word length. This is repeated for each word length from seven (5N1) to 12 (9x1). The one with the highest score is then assumed to be the total word length.

After word length has been established, the software assumes that there is only 1 stop bit and it analyzes the data for the parity bit. If it finds a given parity 100% correct for each of the possible words in the event memory, the communication is deemed to be of that parity. If it finds all the words correctly but mixed parity, it determines there to be no parity. The software could easily be extended to look for more than 1 stop bit.

#### **FUTURE PLANS**

As I developed the QuickComs analyzer, I was amazed at how I was able to take a small sample of data, perform some simple analysis, and have a useful device. I was also amazed at the system's tolerance of errors given the simplicity of both the software and hardware.

I recently began developing the allin-one super RS-232 tool, but sadly, it's still in development. (It's now sitting in some boxes just beside my workbench.) With this latest reincarnation, I hope to integrate all of its existing features with some new ideas. I plan to turn it into a pocket-sized, stand-alone terminal. It will be a technician's best friend.

After graduating in 2001 with a B.E. in electrical and computer engineering from Canterbury University in New Zealand, Nick Lott worked for three and a half years as an electronics technician for Victoria University of Wellington New Zealand. He spent last year exploring Japan and building electronic systems while living in Tokyo and teaching English. Nick currently lives in London. You may contact him at nick.lott@gmail.com.

#### **PROJECT FILES**

To download code and additional files, go to ftp://ftp.circuitcellar.com/pub/

Circuit\_Cellar/2007/198.

#### RESOURCES

J. Axelson, *Serial Port Complete*, Lakeview Research, Madison, WI, 2000.

P. Horowitz and W. Hill, *The Art of Electronics*, Cambridge University Press, Cambridge, England, 1989.

Renesas Technology, M16C Family, Renesas Interactive, www.renesas interactive.com/renesas/guest/guest\_ index.htm.

#### SOURCES

DLP-USB232M USB UART Adapter board DLP Design, Inc. www.dlpdesign.com

LP324N Op-amp National Semiconductor Corp. www.national.com

M16C/62P StarterKit Plus Renesas Technology Corp. www.renesas.com

SN75C3243 IC Texas Instruments, Inc. www.ti.com

## Professional Features – Exceptional Price

34 Channels sampled at 500 MHz Sophisticated Multi-level Triggering Transitional Sampling / Timing and State

Connect this indispensable tool to your PC's USB 1.1 or 2.0 port and watch it pay for itself within hours!

The Atmel AVR Design Contest 2006 Winners Announcement

The Atmel AVR Design Contest 2006 was an excellent opportunity for designers to work with the Atmel AVR family of flash memory microcontrollers and test their

design skills against the world's best and brightest engineers. Last February, designers from all corners of the globe started working with the parts and planning their projects. After thoroughly reviewing each submission, the judges awarded prizes to 12 projects based on their technical merit, usefulness, originality, design optimization, and cost effectiveness.

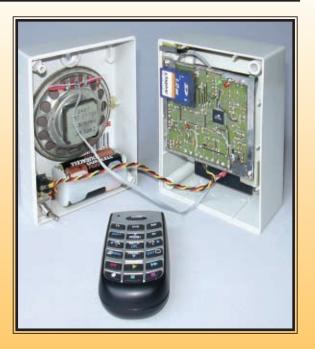

We are proud to announce that Alberto Ricci Bitti has won the Grand Prize for his innovative WITNESSCAM project. Alberto's amazing design is an automated, self-recording surveillance system that features a VGA CMOS camera, a passive infrared movement sensor, a 1-GB SD card, and an Atmel ATmega32 microcontroller. This easy-to-install, self-contained surveillance system is the perfect solution for any building.

Congratulations to all of the winners!

# **GRAND PRIZE**

#### WITNESSCAM

The WITNESSCAM is a self-recording surveillance camera that's perfect for the home or office. The innovative, ATmega32-based system features a VGA CMOS color camera, a passive-infrared (PIR) movement sensor, and a 1-GB SD card. The aesthetically pleasing prototype looks like an ordinary alarm detector, but when it detects movement, it silently starts recording. You can control the system with an infrared remote. The interactive camera responds with voice prompts, and the circuit can recognize when the box is open.

> Alberto Ricci Bitti a.riccibitti@iname.com Italy

## **First Prize**

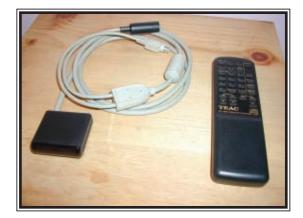

#### ATir AVR IR Keyboard Interface

The well-designed ATtiny45-based ATir interface device offers a convenient cross-platform solution to interface an IR remote control to type keyboard macros to a PC. In addition to the microcontroller, the compact system features an infrared receiver/demodulator and a few discreet components. The interface plugs into a PS2 keyboard port on the PC and accepts commands from an infrared remote.

Steven Savage stevensavage@nls.net U.S.

## **Second Prize**

#### **Bidirectional Stepper Motor**

This interesting ATtiny13-based design takes the principles of current-pulse operated watch hand movement and enables both clockwise and counterclockwise operation. The device, which features a mechanical pointer, provides the altitude indication for a skydiver's altimeter. The pointer mechanism moves in both directions to show altitude on the way up and down.

Chris Belcher stepmotor@ntlworld.com U.K.

# **Third Prize**

#### mOtiOn: A Video-Based Motion Sensor

The mOtiOn is an inexpensive video-based motion sensor. It's based on the real-time processing of a video signal using analog preprocessing and optimized image-processing algorithms in an ATmega88 microcontroller. The unique sensor can detect movement in an incoming composite video signal in real time at 30 frames per second. It also conveniently shows where the movement is detected on its video output.

> Naubert Aparicio naubert.aparicio@usa.net U.S.

## The complete entries are available at www.circuitcellar.com/avr2006/.

# **Honorable Mention**

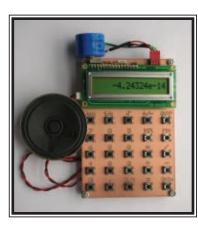

## **Talking Calculator**

This precise, user-friendly, ATmega88-based talking calculator operates with real numbers. It features the four basic operations (addition, subtraction, multiplication, and division) and several useful functions

(e.g., change of sign (+/-), inverse (1/x), add with memory (M+), and read from memory (MR)).

Mariano Barron Ruiz ispbarum@sb.ehu.es Spain

# **Honorable Mention**

#### **Slave Flash Trigger**

A camera's external flash can be triggered remotely with its built-in flash. Unlike "photocells," the

**Honorable Mention**

Built around an ATmega168 microcontroller, this

handy password-managing system enables you to

enter, store, and display numerous passwords and

usernames. The secure device connects to your PC

via a useful software-controlled USB interface.

The Lord of the Keys

ATtiny13-based Slave Flash Trigger is intelligent. It can determine a camera's main flash and synchronize it with the external flash.

> Aleksander Borysiuk alex\_priv@wp.pl Poland

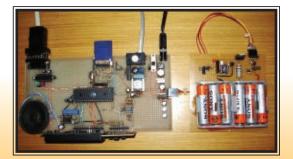

## Honorable Mention AVR Phone Recorder and Telephony Platform

This well-planned, ATmega32-based project demonstrates the implementation of a phone line audio and event recorder that was originally designed for technical support call center quality-assurance purposes. The reasonably generic telephony platform can be easily adapted for other applications, such as an answering machine/interactive voice response system.

> Marco Carnut kiko@tempest.com.br Brazil

*Carlos Cossio* ccossio@hotmail.com Spain

## The complete entries are available at www.circuitcellar.com/avr2006/.

## **Honorable Mention**

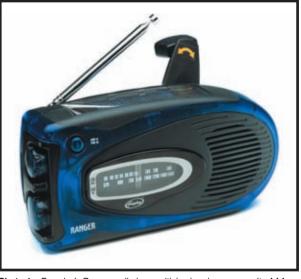

#### SAMEgen

The compact SAMEgen is a test generator for the National Weather Service's Specific Area Message Encoding (SAME) coding. The ATtiny45-based system is useful for both the development of decoding circuitry and the testing of SAME-enabled receivers.

Don L. Jackson don.jackson@ae5k.us U.S.

# **Honorable Mention**

### Dummyload

The simple ATmega169-based Dummyload project simulates loads from 0 to 1,000 mA to help characterize new power supply designs. The system enables you to test at different loading values and test load transients. The microcontroller interfaces with an inexpensive LCD and a joystick to provide a simple user interface.

> klumia@adelphia.net U.S.

#### Doggie 911

The Doggie 911 electronic monitoring system enables dog owners and vets to monitor the patterns of epileptic seizures in dogs. The real-time, ATmega32-based system logs the number of seizures, the duration of the seizures, and the time

between seizures so that veterinarians can better diagnose and treat epilepsy.

> Steve Lubbers ke8fp@arrl.net U.S.

# **Honorable Mention**

## Automatic Egg Incubator

The easy-to-use ATmega32-based Automatic Egg Incubator facilitates the proper hatching of healthy birds. Two digital thermometer chips serve as dry and wet electronic thermometers. An LCD shows the real-time status of the system, which rotates the eggs and monitors variables such as temperature, aeration, and humidity.

> Niyaz K. Zubair nkz1984@yahoo.com India

Kenneth Lumia

## The complete entries are available at www.circuitcellar.com/avr2006/.

# Multi-Input Temperature Logger

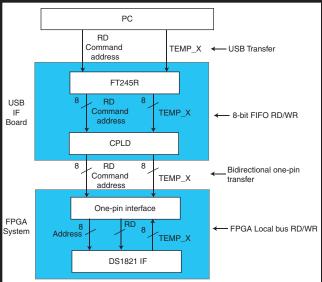

Nial designed an FPGA-based multiple-input temperature logger with an innovative USB interface. In this article, he describes the FPGA logic to drive the sensors and the flexible one-pin USB interface used to connect it to a PC.

Wouldn't it be useful to be able to monitor a number of temperatures simultaneously? I want to be able to measure the temperature in my house, determine the temperature in my refrigerator, verify the internal temperatures in my designs, measure the temperature under the hood of a car I'm tuning up, and more.

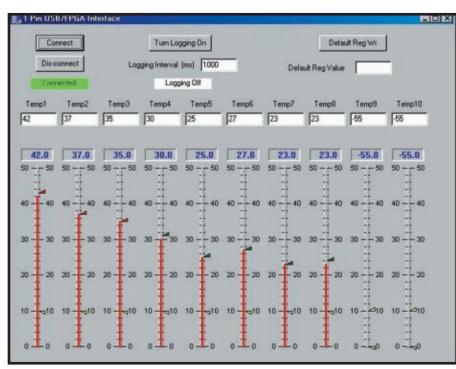

I recently came across some inexpensive temperature sensors with an easyto-drive 1-Wire interface, so I built a system for measuring and logging a number of temperatures. The system can measure more than eight inputs between  $-10^{\circ}$  to  $100^{\circ}$ C. In addition, it can measure temperatures from a distance (my garage is at the other end of the house). When I interface the system to a PC, I can easily view the data. I kept the logic footprint per sensor low, so I could see how many sensors could be driven from one FPGA.

My background is in digital design (with a very strong emphasis on FPGA design/implementation for the last 12 years or so). As the saying goes, "When your only tool is a hammer, everything

looks like a nail." An FPGA seemed like the obvious choice for the project. My immediate thought was to use an FPGA evaluation board, so all I had to worry about was the logic.

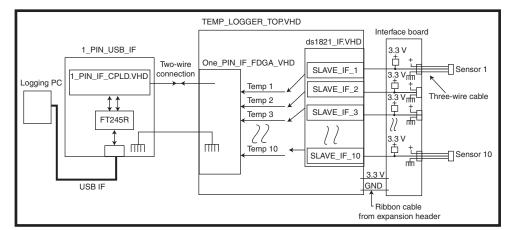

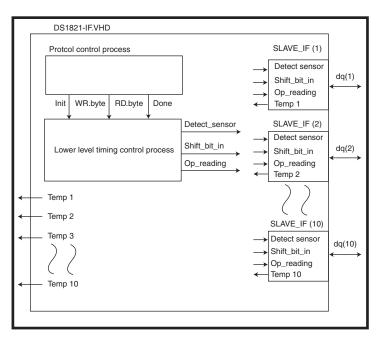

In this article, I'll describe the system and my test results. I'll concentrate on the the FPGA logic to drive the sensors and the flexible one-pin USB interface used to connect it to a PC (see Figure 1).

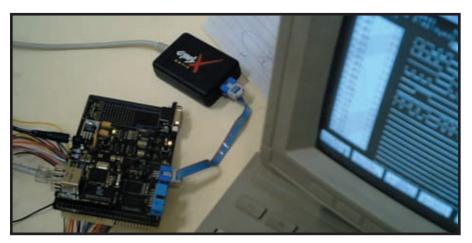

#### **FPGA BOARD**

The logic required to drive

the sensors and implement the USB interface is not that complex. Most modern FPGAs and some larger CPLDs would have done the job. I had an Altera Nios (Altera's soft core processor) evaluation board on hand. This is built around an Altera EP1C20F400C7. In addition to the onboard components required for Nios experiments, it also has two sets of expansion headers that enable an easy connection straight to the FPGA. Although it was complete overkill for what I needed, I pressed it into service (see Photo 1).

#### **TEMPERATURE MEASUREMENT**

As I was flicking through some catalogs, I found a wide range of temperature sensors. I wanted one with a simple digital output so I could drive as many as possible with the aforementioned accuracy and input range. The relatively inexpensive Maxim DS1821 digital thermostat and thermometer (approximately \$6) seemed to meet all of my criteria. 1-Wire, but it seems to use a particular flavor of the 1-Wire interface. My understanding is that most 1-Wire applications allow devices to be addressed on a common interface, whereas the DS1821 allows only point-to-point wiring. It might have been convenient to be able to run a single cable run to remote sensors, but each DS1821 requires only three interface cables, so this isn't a big drawback.

#### 1-Wire/DS1821

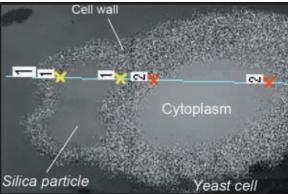

The 1-Wire interface relies on a data line pulled high with a resistor at some point. All communication is performed by pulling the line down to signal 0 or releasing it to signal 1. When communicating with the DS1821, the FPGA is considered the master and the DS1821 is the slave.

All communication with the DS1821 starts with an initialization sequence where the master pulls the data line low for more than 480 µs and then releases the line. After a period of time, the slave pulls the line low for 60 to 240 µs to confirm that it's

The DS1821 interface is described as

Figure 1—Temp\_logger\_top.vhd is implemented on the FPGA evaluation board. The other two modules are small custom PCBs.

Photo 1—Take a look at the entire system. The one-pin interface board is on the right. The sensor interface board is at the bottom. Only four sensors (two are shown) are wired in.

present. The command byte or data byte transfer sequence follows the initialization.